Multi-core chips are currently in the spotlight as a potential means to overcome the limits of frequency scaling for performance increases in processors. In this direction, the CSA group at the University of Amsterdam is investigating a new design for processors towards faster and more efficient general-purpose multi-core chips. However this design changes the interface between the hardware and software, compared to existing chips, in ways that have not been dared previously. Consequently, the concepts underlying existing operating systems and compilers must be adapted before this new design can be fully integrated and evaluated in computing systems.

This dissertation investigates the impact of the changes in the machine interface on operating software and makes four contributions. The first contribution is a comprehensive presentation of the design proposed by the CSA group. The second contribution is formed by technology that demonstrates that the chip can be programmed using standard programming tools. The third contribution is a demonstration that the hardware components can be optimized by starting to implement operating software during the hardware design instead of afterwards. The fourth contribution is an analysis of which parts of the hardware design will require further improvements before it can be fully accepted as a generalpurpose platform. The first conclusion is a confirmation that the specific design considered can yield higher performance at lower cost with relatively minimal implementation effort in software. The second conclusion is that the processor interface can be redefined while designing multi-core chips as long as the design work is carried out hand in hand with operating software providers.

On the realizability of hardware microthreading Raphael 'kena Poss

# On the realizability of hardware microthreading Revisiting the general-purpose processor interface:

Revisiting the general-purpose processo consequences and challenges

Raphael 'kena' Poss

# Uitnodiging

Voor het bijwonen van de openbare verdediging van mijn proefschrijft:

On the realizability of hardware microthreading

Woensdag 5 september 2012 om 10:00

Anietenkapel Oudezijds Voorburgwal 231 1012 EZ Amsterdam

#### Stellingen

behorende bij het proefschrift

#### On the realizability of hardware microthreading

- 1. General-purpose computers are, like stem cells for living organisms, key to the perpetuation of computer engineering. (Chapter 1)

- 2. Het samenstellen van verwerkingseenheden eerder ontworpen voor alleenstaand gebruik leidt tot een minder efficiënt multi-processor ontwerp. (Deel I & III)

- 3. Ingenuity and expediency are effective complements to analysis and synthesis. (Chapter 6)

- 4. De menselijke acceptatie van wijzigingen in de softwareinterface van verwerkingseenheden vereist een voorzichtige deconstructie van voormalige aannames en modellen; de bijbehorende aanpassingen in besturingssoftware zijn in vergelijking triviaal. (Deel II)

- 5. Amdahl's suggestion for a balanced design, i.e. a chip should provision a bit per second of external bandwidth for every instruction per second, should also apply to the bandwidth between any two individual hardware threads in multiprocessors. (Chapters 9 & 13)

- 6. Creativiteit en ijver zijn zelden samen aanwezig in één individu; het succesvolle uitbrengen van innovatie in informatica vereist dus een symbiose tussen verschillende persoonlijkheden. (Dit proefschrift en het hele gebied van computerarchitectuur)

- 7. The advent of general-purpose computers has altered the limitations of the human condition in ways both unforeseen and still poorly understood.

- 8. Het theoretische bestuderen van programmeertalen en computermodellen levert alleen kennis op over hoe mensen nadenken, niet over het gedrag van programma's.

- 9. Free and unencumbered information duplication is currently our sole means to avoid a digital dark age and leave a trace in history.

- 10. Videospelletjes en hun beleving door spelers zullen worden erkend door toekomstige historici als een baanbrekende nieuwe kunstvorm en een van de grootste prestaties van de mensheid.

### On the realizability of hardware microthreading

Revisiting the general-purpose processor interface: consequences and challenges

This research was supported by the European Union under grant numbers FP7-215216 (Apple-CORE) and FP7-248828 (ADVANCE).

Copyright © 2012 by Raphael 'kena' Poss, Amsterdam, The Netherlands.

This work is licensed under the Creative Commons Attribution-Non-Commercial 3.0 Netherlands License. To view a copy of this license, visit the web page at http://creativecommons.org/licenses/by-nc/3.0/nl/

or send a letter to Creative Commons, 444 Castro Street, Suite 900, Mountain View, California, 94041, USA.

Cover photograph by Éole Wind - http://eole.me

Typeset by IAT<sub>E</sub>X. Printed and bound by Gildeprint Drukkerijen.

ISBN: 978-94-6108-320-3

### On the realizability of hardware microthreading

Revisiting the general-purpose processor interface: consequences and challenges

ACADEMISCH PROEFSCHRIFT

ter verkrijging van de graad van doctor aan de Universiteit van Amsterdam op gezag van de Rector Magnificus prof. dr. D.C. van den Boom ten overstaan van een door het college voor promoties ingestelde commissie, in het openbaar te verdedigen in de Agnietenkapel op woensdag 5 september 2012, te 10:00 uur

door

Raphael 'kena' Poss

geboren te Aix-en-Provence, Frankrijk.

Promotiecommissie:

| Promotor:      | Prof. dr.               | C.R. Jesshope                                                                              |

|----------------|-------------------------|--------------------------------------------------------------------------------------------|

| Overige leden: | Dr.<br>Dr.<br>Prof. dr. | M. Brorsson<br>B. Chamberlain<br>C.U. Grelck<br>P. Klint<br>C.T.A.M. de Laat<br>SB. Scholz |

Faculteit der Natuurwetenschappen, Wiskunde en Informatica

Even if there needs to be a shift at some point from the user's perspective—your goal is to make that shift as smooth as possible.

Daniel Prokesch

## Contents

| Co                             | ntents                                                 | i   |

|--------------------------------|--------------------------------------------------------|-----|

| $\mathbf{Lis}$                 | t of Figures                                           | iii |

| Lis                            | t of Tables                                            | vii |

| Lis                            | t of Side Notes                                        | ix  |

| Listings                       |                                                        | xi  |

| Summary                        |                                                        | 1   |

| Samenvatting in het Nederlands |                                                        | 5   |

| Acknowledgements               |                                                        | 9   |

| Pre                            | face                                                   | 11  |

| 1                              | Introduction                                           | 15  |

| Ι                              | Hardware microthreading: exploring the designer's mind | 31  |

| <b>2</b>                       | Trade-offs in microprocessor design                    | 33  |

| 3                              | Architecture overview                                  | 43  |

| 4                              | Machine model & hardware interface                     | 59  |

| Π                              | Foreground contribution: programmability               | 81  |

| 5                              | System perspective                                     | 83  |

| 6                              | Programming environment                                | 97  |

| 7                              | Disentangling memory and synchronization               | 115 |

| 8                              | Visible synchronizer windows                           | 137 |

| 9                              | Thread-local storage                                   | 147 |

| 10                             | Concurrency virtualization                             | 163 |

| 11                             | Placement and platform partitioning                    | 175 |

| <b>12</b>                      | Issues of generality                                   | 187 |

| III            | Applications and experiences                   | <b>201</b> |

|----------------|------------------------------------------------|------------|

| <b>13</b>      | Core evaluation                                | 203        |

| <b>14</b>      | System-level issues                            | 223        |

| 15             | Conclusions and future work                    | 235        |

| 16             | Epilogue on the outer question                 | 243        |

| IV             | Appendices                                     | 247        |

| $\mathbf{A}$   | Information sources for the hardware interface | <b>249</b> |

| в              | Optimal control word size analysis             | 251        |

| $\mathbf{C}$   | Running example with machine code              | 253        |

| D              | Machine instructions                           | 259        |

| $\mathbf{E}$   | On-chip placement and distribution             | 263        |

| $\mathbf{F}$   | Semantics of C objects                         | 269        |

| $\mathbf{G}$   | Original language interface                    | 277        |

| н              | Approach to code generation                    | 293        |

| Ι              | SL Language specification                      | 317        |

| J              | QuickSort example                              | 333        |

| К              | Mandelbrot set approximation                   | 339        |

| Acr            | conyms                                         | 341        |

| $\mathbf{Rel}$ | ated publications by the author                | 343        |

| $\mathbf{Bib}$ | liography related to hardware microthreading   | 345        |

| Gei            | neral bibliography                             | 349        |

| Index          |                                                | 367        |

## List of Figures

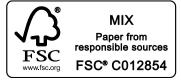

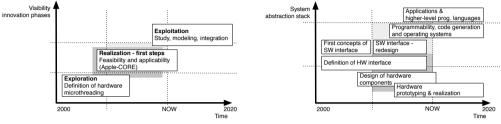

| $1.1 \\ 1.2 \\ 1.3$                                         | Activities related to science                                                                                                                                                                                               | 17<br>18<br>30                                                              |

|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

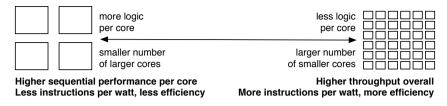

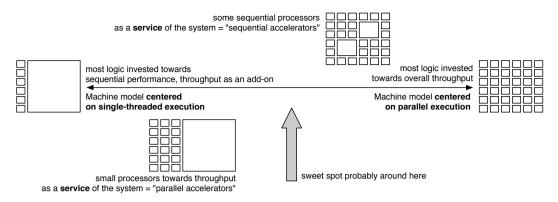

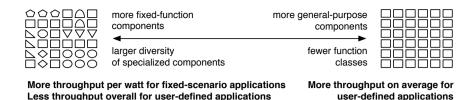

| $2.1 \\ 2.2 \\ 2.3$                                         | Choice between smaller or larger cores at equal logic and energy budget<br>Room for sequential performance at equal area and energy budget Choice between specialized functions or general-purpose cores at equal logic and | 35<br>36                                                                    |

|                                                             | energy budget.                                                                                                                                                                                                              | 37                                                                          |

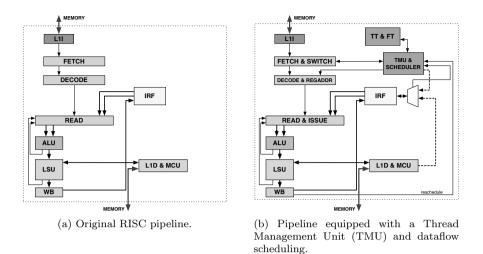

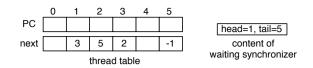

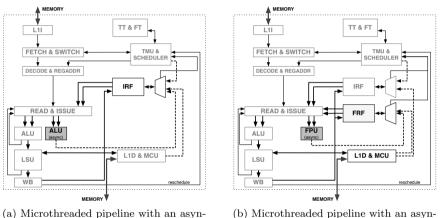

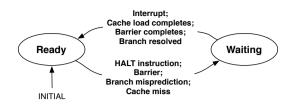

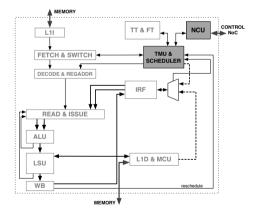

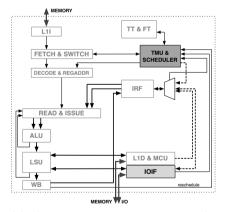

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9 | Microthreaded extensions on a typical in-order, single-issue 6-stage RISC pipeline.<br>Example suspended thread list                                                                                                        | $\begin{array}{c} 45 \\ 46 \\ 49 \\ 49 \\ 50 \\ 50 \\ 54 \\ 57 \end{array}$ |

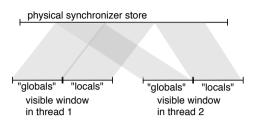

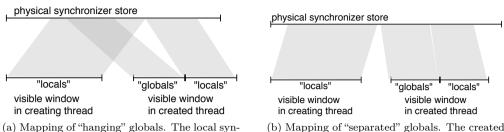

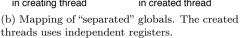

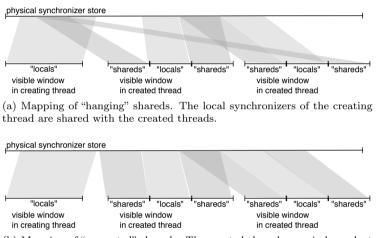

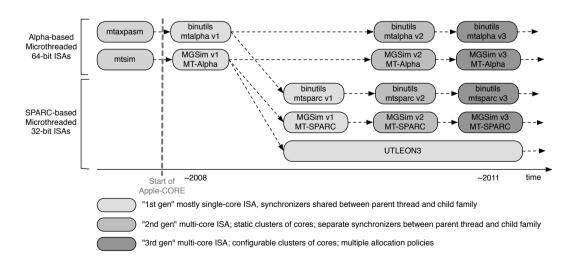

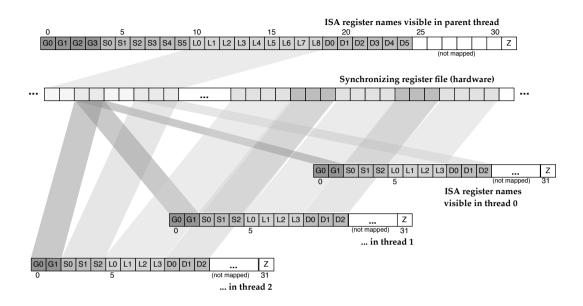

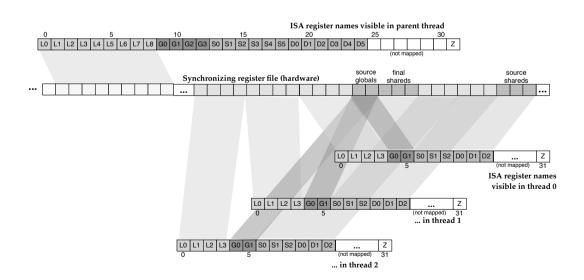

| 4.1<br>4.2                                                  | Example window mapping for two sibling threads with global and local synchro-<br>nizers                                                                                                                                     | 68                                                                          |

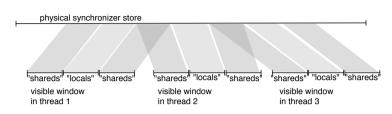

| $4.3 \\ 4.4 \\ 4.5$                                         | chronizers                                                                                                                                                                                                                  | 69<br>70<br>70<br>78                                                        |

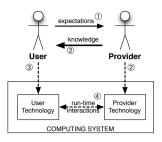

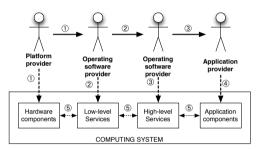

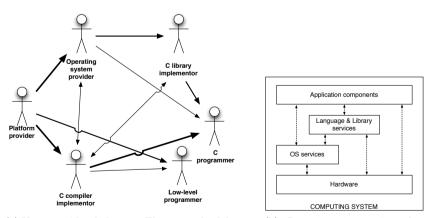

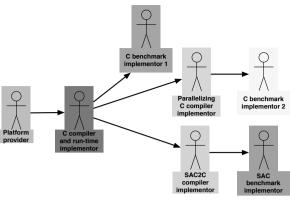

| $5.1 \\ 5.2 \\ 5.3 \\ 5.4 \\ 5.5 \\ 5.6$                    | User-provider relationship in a computing ecosystem                                                                                                                                                                         | 86<br>86<br>90<br>93<br>93                                                  |

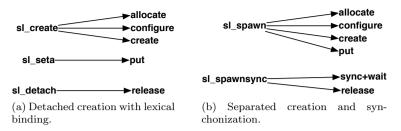

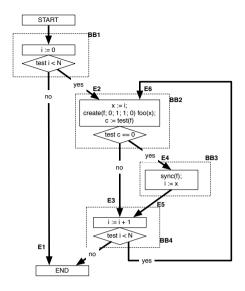

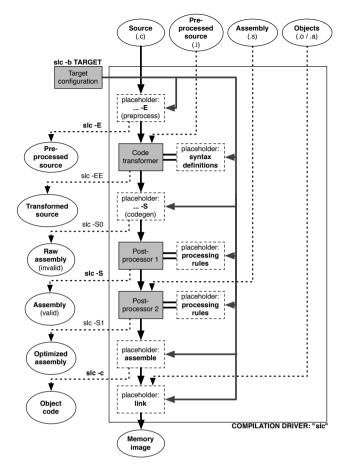

| $6.1 \\ 6.2 \\ 6.3$                                         | Overview of the placeholders in the SL tool driver                                                                                                                                                                          | $103 \\ 104 \\ 105$                                                         |

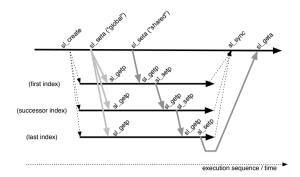

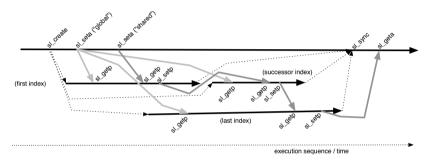

| $\begin{array}{c} 6.4 \\ 6.5 \end{array}$ | Example uses of sl_createsl_sync                                                                                                                                | $\begin{array}{c} 107 \\ 108 \end{array}$ |

|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

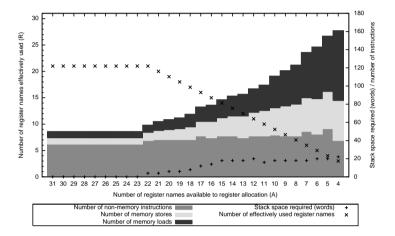

| $8.1 \\ 8.2$                              | Register allocation as a function of the number of available register names<br>Effect of various numbers of available register names on the outcome of register | 140                                       |

|                                           | allocation with a simple function updating a variable in memory                                                                                                 | 140                                       |

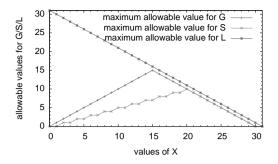

| 8.3                                       | Maximum allowable values of $G, S, L$ for various values of $X$ , with $M = 31$                                                                                 | 143                                       |

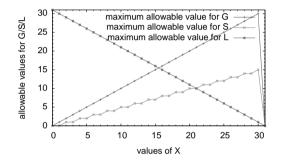

| 8.4                                       | Maximum allowable values of $G, S, L$ for various values of $X$ , with $M = 31$                                                                                 | 144                                       |

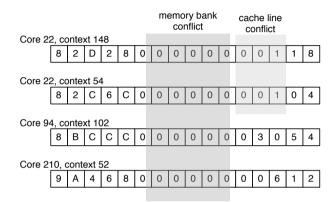

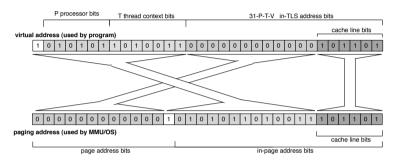

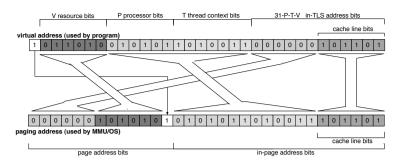

| 9.1                                       | Potential bank and line conflicts with 64-bit addresses, 1024 cores, 256 contexts                                                                               | 154                                       |

| 9.2                                       | per core                                                                                                                                                        | 154<br>155                                |

| 9.2<br>9.3                                | Reduced TLS address conflicts with XOR-based randomization.                                                                                                     | $155 \\ 155$                              |

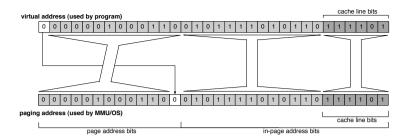

| 9.3                                       | Address bit shuffling for non-TLS pages.                                                                                                                        | 156                                       |

| 9.5                                       | Address bit shuffling to aggregate distinct small TLS spaces into shared physical                                                                               |                                           |

| 0.0                                       | pages                                                                                                                                                           | 156                                       |

| 9.6                                       | Address bit shuffling for non-TLS pages (virtual processes)                                                                                                     | 158                                       |

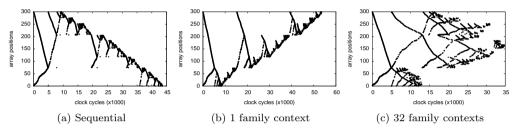

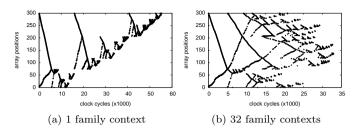

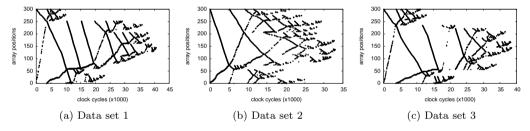

| 10.1                                      | Execution of QuickSort on 1 core                                                                                                                                | 171                                       |

| 10.2                                      | Execution of QuickSort on 1 core (threshold: 16 elements)                                                                                                       | 172                                       |

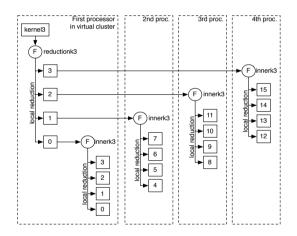

| 11.1                                      | Parallel reduction using explicit placement, for problem size $n = 16$ and a virtual                                                                            |                                           |

|                                           | core cluster containing 4 cores                                                                                                                                 | 179                                       |

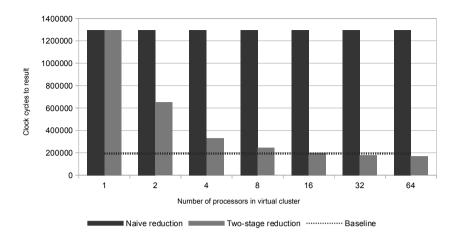

| 11.2                                      | Performance of the Livermore loop 3                                                                                                                             | 181                                       |

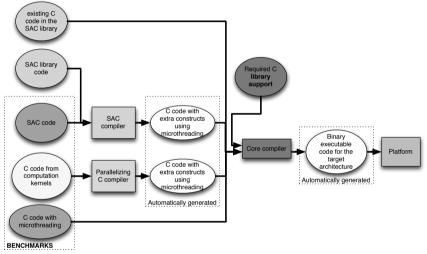

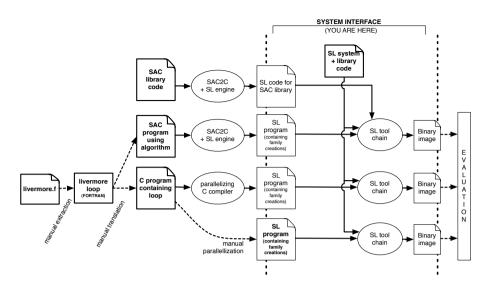

| 13.1                                      | Implementing the Livermore loop benchmarks using our proposed framework                                                                                         | 206                                       |

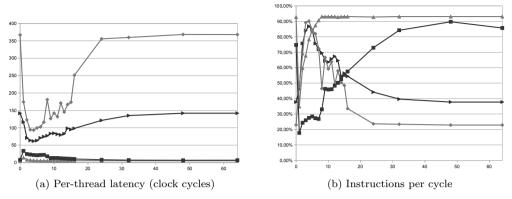

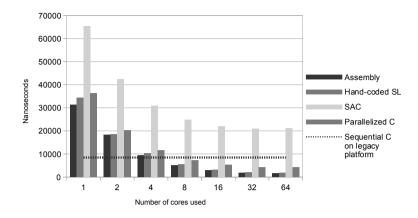

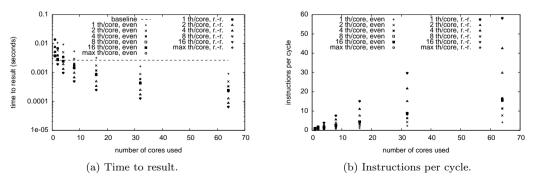

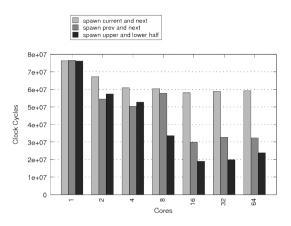

|                                           | Time to result (performance) for the Livermore loop 7                                                                                                           | 208                                       |

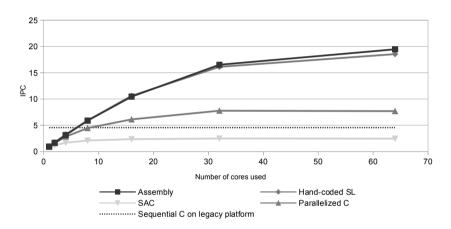

|                                           | Instructions per cycle (utilization) for the Livermore loop 7                                                                                                   | 208                                       |

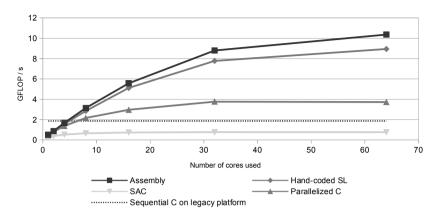

|                                           | Floating-point performance for the Livermore loop 7                                                                                                             | 209                                       |

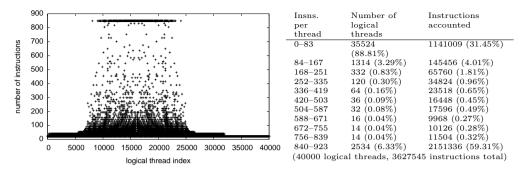

|                                           | Actual thread sizes in the example heterogeneous workload                                                                                                       | 211                                       |

|                                           | Performance of the example heterogeneous workload.                                                                                                              | 211                                       |

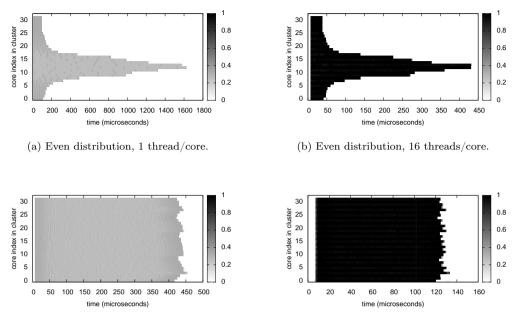

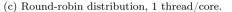

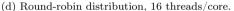

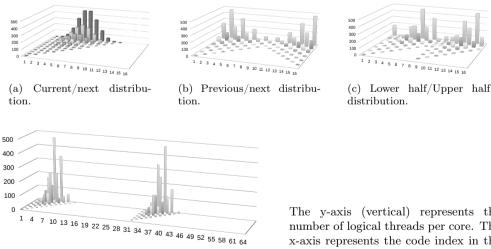

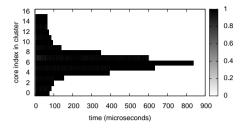

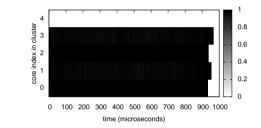

|                                           | Per-core activity for the example heterogeneous workload running on 32 cores.                                                                                   | 212                                       |

|                                           | QuickSort performance on the proposed platform.                                                                                                                 | 214                                       |

|                                           | Different logical thread distributions for QuickSort.                                                                                                           | 214                                       |

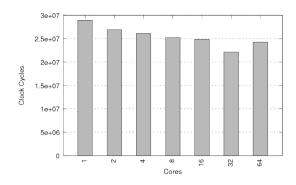

|                                           | QuickSort performance using automatic load balancing                                                                                                            | 215                                       |

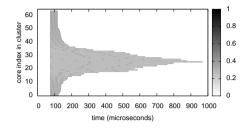

|                                           | Per-core activity for the example heterogeneous workload with a 1ms deadline.                                                                                   | 216                                       |

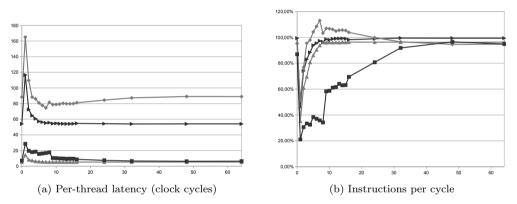

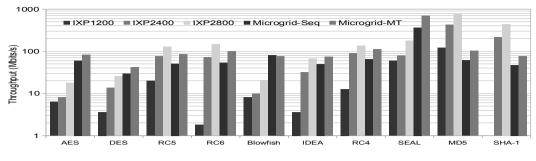

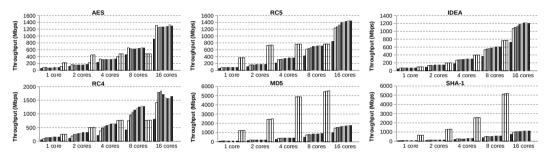

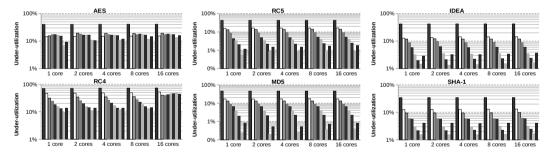

|                                           | 27 Throughput for one stream on one core                                                                                                                        | 217<br>217                                |

|                                           | Combined throughput for 1-8,16 streams per core on 1-16 cores                                                                                                   |                                           |

| 15.14                                     | 4Pipeline under-utilization for fig. 13.13.                                                                                                                     | 217                                       |

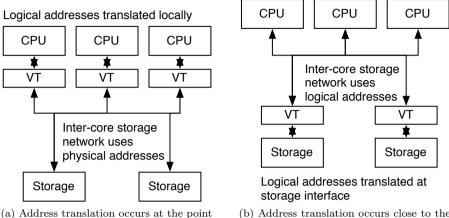

| 14.1                                      | Possible locations for the address translation logic on chip                                                                                                    | 227                                       |

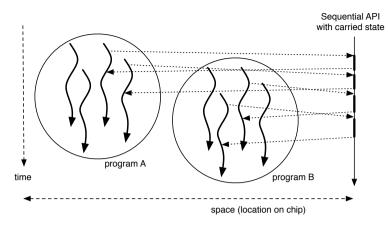

| 14.2                                      | Forced synchronization through sequential APIs                                                                                                                  | 230                                       |

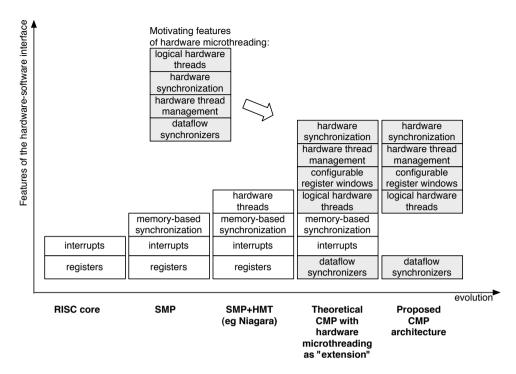

| 15.1                                      | Features of the machine interface across CMP designs                                                                                                            | 237                                       |

| C.1                                       | Observed synchronizer sharing between a creating thread and a family of 3 threads                                                                               | .258                                      |

| C.2                                       | Observed register sharing between a creating thread and a family of 3 threads                                                                                   | 258                                       |

| G.1                                       | Control flow graph of the function "bar" in listing G.8                                                                                                         | 291                                       |

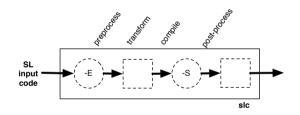

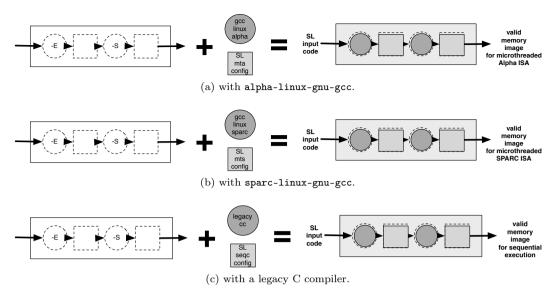

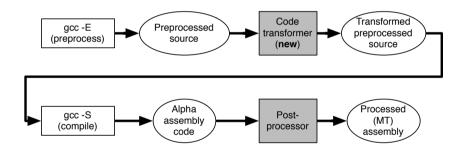

| H.1 | Position of the assembly post-processor in the tool chain                        | 295 |

|-----|----------------------------------------------------------------------------------|-----|

| H.2 | Position of the code transformer in the tool chain                               | 299 |

| H.3 | The "slc" compilation pipeline and driver.                                       | 315 |

| I.1 | Channel topology in a parallel thread family                                     | 331 |

| I.2 | Channel topology in a thread family with irregular schedule                      | 331 |

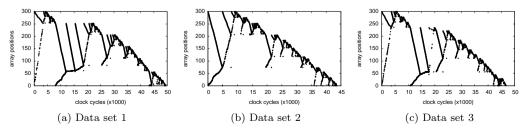

| J.1 | Baseline: purely sequental algorithm as one thread                               | 333 |

| J.2 | Execution on 1 core with 1 family context.                                       | 336 |

| J.3 | Execution on 1 core with 3 family contexts.                                      | 336 |

| J.4 | Execution on 1 core with 31 family contexts.                                     | 337 |

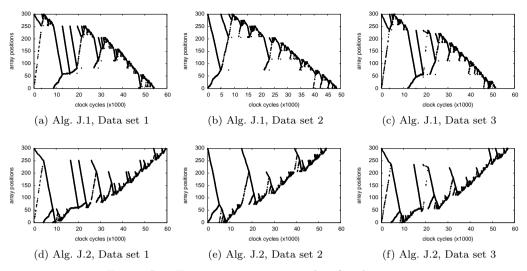

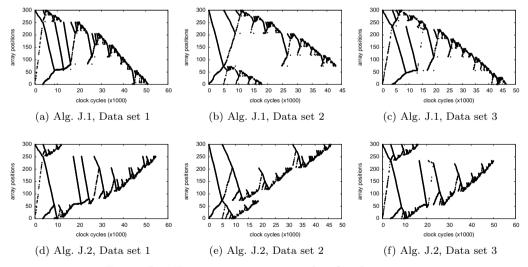

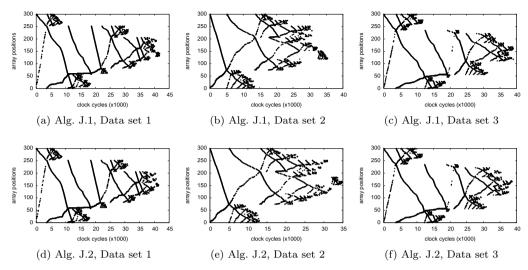

|     | Execution on 1 core with 31 family contexts, using Algorithm J.1 and a threshold |     |

|     | on concurrency creation.                                                         | 337 |

## List of Tables

| $1.1 \\ 1.2$                    | Symbols used to mark technical contributions throughout our dissertation<br>Overview of technical contributions per chapter       | $\begin{array}{c} 29\\ 30 \end{array}$ |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| $3.1 \\ 3.2 \\ 3.3$             | Control events to the TMU.                                                                                                        | 57<br>58<br>58                         |

| $4.1 \\ 4.2$                    | Features of existing general-purpose RISC ISAs                                                                                    | 74<br>78                               |

| 5.1                             | Possible target ecosystems for the proposed architecture                                                                          | 89                                     |

| $6.1 \\ 6.2$                    | Main constructs of the resulting SL language                                                                                      | 104<br>112                             |

| 8.1                             | Calling conventions on existing general-purpose processors                                                                        | 144                                    |

| 9.1<br>9.2<br>9.3<br>9.4<br>9.5 | Trade-offs of context-based TLS partitioning                                                                                      | 152<br>153<br>154<br>157<br>161        |

| 11.1                            | Core addressing operators in the SL library                                                                                       | 178                                    |

| 13.1                            | System characteristics                                                                                                            | 209                                    |

| 14.1                            | Implicitly carried dependencies in C/POSIX APIs                                                                                   | 229                                    |

| A.1<br>A.2                      | Example programs from the architecture test suite, December 2008 Academic publications explaining the architecture, December 2008 | $250 \\ 250$                           |

| B.1<br>B.2                      | Impact of control bits on I-cache line utilization                                                                                | 251<br>251                             |

| C.1<br>C.2                      | Memory image for the program "fibo", late 2008                                                                                    | $253 \\ 256$                           |

| D.1                             | Description of the family control instructions.                                                                                   | 259                                    |

| Description of the register-to-register communication instructions                | 260                                                      |

|-----------------------------------------------------------------------------------|----------------------------------------------------------|

| Description of the bulk context management instructions                           | 260                                                      |

| Description of miscellaneous instructions.                                        | 260                                                      |

| MT instruction set extensions implemented in UTLEON3                              | 260                                                      |

| General MT extensions for a SPARC v8 instruction set.                             | 261                                                      |

| MT extensions for the DEC/Alpha AXP 24264 instruction set                         | 262                                                      |

| Address transformation for allocation messages on chip                            | 265                                                      |

| Execution cost of the placement primitives                                        | 267                                                      |

| Example programs using the proposed C extensions, December 2008                   | 278                                                      |

| Academic publications related to the C language extensions, December 2008 $\ .$ . | 278                                                      |

| Substitution table for register names                                             | 297                                                      |

| Substitution table for FP register names.                                         | 311                                                      |

| Supported compilation targets at the time of publication of this book             | 316                                                      |

|                                                                                   | Description of the bulk context management instructions. |

## List of Side Notes

| 1.1  | Fundamental sciences are also application-driven             |

|------|--------------------------------------------------------------|

| 1.2  | The second rise of separated computing                       |

| 1.3  | Embedded/specialized vs. general-purpose computers           |

| 1.4  | Example functions that can be made primitive recursive       |

| 1.5  | Example functions that are not primitive recursive           |

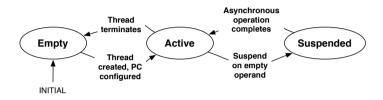

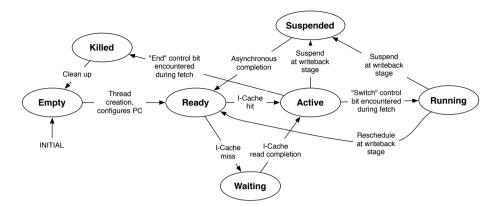

| 3.1  | Active, ready and waiting queues                             |

| 3.2  | New instruction vs. control bits for thread termination      |

| 3.3  | Fine-grained thread states                                   |

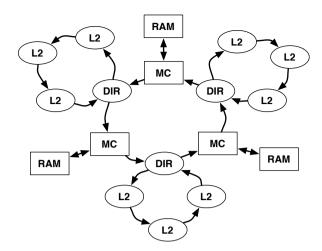

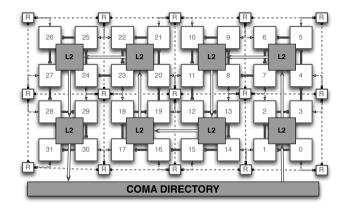

| 3.4  | Using a distributed cache between microthreaded cores        |

| 3.5  | Sub-events for remote creations                              |

| 4.1  | Logical index sequence                                       |

| 4.2  | Purpose and motivation of "shared" synchronizers             |

| 4.3  | Thread switching not specified by control bits               |

| 4.4  | Switching and thread termination as instructions             |

| 6.1  | Contenders to C to pitch new architectural designs           |

| 7.1  | About implicit communication                                 |

| 9.1  | Support for heap-based dynamic allocation                    |

| 10.1 | Static vs. dynamic allocation failure management             |

| 12.1 | Implementation-independent interleaving                      |

| 13.1 | About the relevance of the Livermore loops                   |

| 13.2 | Description of the example heterogeneous workload            |

| 13.3 | Choice of QuickSort for evaluation                           |

| E.1  | Processor address decoding in the reference implementation   |

| E.2  | About the distribution of families with "shared" channels    |

| F.1  | About the concept of objects in the C language specification |

| F.2  | About immutable objects                                      |

| F.3  | About objects without an address                             |

| F.4  | About object sizes                                           |

| F.5  | About array item properties                            | 271 |

|------|--------------------------------------------------------|-----|

| F.6  | About multiple accesses between sequence points.       | 271 |

| F.7  | About the initial char representation of objects.      | 271 |

| F.8  | About valid addresses one past the last char           | 271 |

| F.9  | Objects without primary designators                    | 273 |

| F.10 | Primary designator aliases for immutable objects.      | 273 |

| F.11 | About array designators in function parameter lists    | 274 |

| G.1  | Attempt to constrain the well-formedness of programs   | 283 |

| G.2  | About the input availability of "shareds" after writes | 286 |

| H.1  | About the avoidance of a C syntax parser               | 300 |

| H.2  | Preservation of line number markers in M4              | 300 |

| I.1  | About the compatibility of our implementation.         | 319 |

| I.2  | About the syntax of "sl_create" and "sl_sync"          | 328 |

| I.3  | About pointers to thread functions                     | 328 |

| I.4  | Defining the index sequence in the abstract semantics. | 330 |

## Listings

| 7.1          | Two unrelated threads.                                                                           | 127          |

|--------------|--------------------------------------------------------------------------------------------------|--------------|

| $7.2 \\ 7.3$ | Two unrelated threads with a race condition                                                      | 128<br>128   |

| $7.3 \\ 7.4$ | Implementation of twoprint, insufficiently synchronized                                          | 128          |

| $7.4 \\ 7.5$ | Proper synchronization for twoprint.                                                             | $129 \\ 129$ |

| 7.6          | Invalid busy waiting for a value.                                                                | 129 129      |

| 7.7          | Invalid busy waiting on a pointer.                                                               | 130          |

| 8.1          | Code fragment using multiple virtual "global" channels                                           | 145          |

| 8.2          | Translation of listing 8.1 to use only one "global" channel                                      | 145          |

| 9.1          | Code sequence to access TLS on UTLEON3                                                           | 160          |

|              | Automatic serialization code for listing H.21 (simplified)                                       | 168          |

| 10.2         | Generated assembly code for listing 10.1                                                         | 169          |

| 11.1         | Concurrent SL code for the Livermore loop 3 (inner product)                                      | 179          |

| 11.2         | Concurrent SL code for the Livermore loop 3, optimized                                           | 180          |

|              | FORTRAN code for the Livermore loop 7                                                            | 205          |

|              | Sequential C code for the Livermore loop 7                                                       | 206          |

|              | SAC code for the Livermore loop 7                                                                | 206          |

| 13.4         | Concurrent SL code for the Livermore loop 7                                                      | 207          |

| E.1          | Placement computation that extracts the size from a virtual cluster address.                     | 266          |

| E.2          | Placement computation that extracts the absolute address of the first core in a virtual cluster. | 967          |

| E.3          | Placement computation that divides the current cluster in two and addresses                      | 267          |

| 1.0          | either the upper or lower half                                                                   | 267          |

| E.4          | Placement computation to place all the created thread at a core offset $P$                       | 201          |

|              | within the local cluster.                                                                        | 267          |

| E.5          | Placement computation that divides the current cluster in two and addresses                      |              |

|              | the other half relative to the current core                                                      | 268          |

| E.6          | Placement computation to place all the created thread at the next or previous                    | 0.00         |

|              | core within the local cluster                                                                    | 268          |

| F.1          | Const designator to a mutable object.                                                            | 276          |

|              |                                                                                                  |              |

| G.1  | Example code using the "create" construct and separate thread function to          |            |

|------|------------------------------------------------------------------------------------|------------|

|      | scale a vector                                                                     | -          |

| G.2  | Example thread program using a channel interface specification. $\ldots \ldots 28$ | 30         |

| G.3  | Example use of the "innerprod" thread program                                      |            |

| G.4  | Using the "address of" operator on a channel endpoint                              |            |

| G.5  | Pointer aliasing a channel endpoint                                                | 37         |

| G.6  | Implicit endpoint type conversion                                                  | 38         |

| G.7  | Multiple orderings of the same endpoint names                                      | 38         |

| G.8  | Example program fragment using "create" 29                                         | <b>)</b> 0 |

| G.9  | Example program fragment using the "create" construct                              | <i>)</i> 2 |

| H.1  | Hand-crafted thread program                                                        | <b>)</b> 4 |

| H.2  | Hand-crafted C code                                                                | <b>)</b> 4 |

| H.3  | Alpha assembly generated using GNU CC                                              |            |

| H.4  | C code with strategically placed macro uses                                        |            |

| H.5  | Macro definitions for thread programs                                              |            |

| H.6  | Externally instrumented Alpha assembly                                             |            |

| H.7  | Automatically edited Alpha assembly                                                |            |

| H.8  | Edited Alpha assembly with fewer used local registers                              |            |

| H.9  | Macro definitions necessary for different interface arities                        |            |

|      | Code using multiple channel endpoints                                              |            |

|      | Generated assembly source for the "scal" thread program                            |            |

|      | Source code for the "innerprod" thread program                                     |            |

|      | Generated assembly for the "innerprod" thread program                              |            |

|      | Prototype "create" construct                                                       |            |

|      | Example use of "createsync."                                                       | )4         |

|      | Generated asembly from listing H.15                                                |            |

|      | Example use of "createsync" with omitted parameters                                |            |

|      | Generated assembly for listing H.17                                                |            |

|      | Support for "global" channel endpoints in "createsync."                            |            |

|      | Extension of listing H.19 for "shared" channels                                    | )6         |

| H.21 | Example vector-vector product kernel                                               |            |

|      | Generated code for listing H.21, using the "fused" creation interface 30           |            |

|      | Generated code for listing H.21, using the "detached" creation interface 31        | -          |

|      | Syntax expansions for a sequential schedule                                        |            |

|      | Substitution for SPARC's save                                                      |            |

|      | Substitution for SPARC's restore                                                   |            |

| T 1  | QuickSort benchmark in SL, classic algorithm                                       | ) /        |

| J.1  |                                                                                    |            |

| J.2  | QuickSort benchmark in SL, families of two threads                                 | ю          |

| K.1  | Computation kernel executed by each logical thread 35                              | 39         |

| K.2  | Workload implementation using an even distribution                                 | 39         |

| K.3  | Workload implementation using a round-robin distribution                           | 10         |

### Summary

Ever since the turn of the century, fundamental energy and scalability issues have precluded further performance improvements in general-purpose uniprocessor chips. To "cut the Gordian knot," [RML<sup>+</sup>01] the industry has since shifted towards multiplying the number of processors on chip, creating increasing larger Chip Multi-Processors (CMPs) by processor counts, to take advantage of efficiency gains made possible by frequency scaling [RML<sup>+</sup>01, SA05]. Yet so far most general-purpose multi-core chips have been designed by grouping together processor cores that had been originally designed for single core, mostly single-threaded processor chips. After a decade of renewed interest in CMPs, the architecture community is barely coming to terms with the realization that traditional cores do not compose to create easily programmable general-purpose multi-core platforms.

Instead, the Computer Systems Architecture group at the University of Amsterdam proposes a general machine model and concurrency control protocol, relying on a novel individual core design with dedicated hardware support for concurrency management across multiple cores [PLY<sup>+</sup>12]. The key features of the design, described as "hardware microthreading," are asynchrony, i.e. the ability to tolerate operations with irregular and long latencies, fine-grained hardware multithreading, a scale-invariant programming model that captures clusters on chip of arbitrary sizes as single programming resources, and the transparent performance scaling of a single binary code across multiple cluster sizes. Its machine interface does not only provide native support for dataflow synchronisation and imperative parallel programming; it also departs from the traditional RISC vision by allowing programs to configure the number of hardware registers available by thread, replacing interrupts by thread creation as a means to signal asynchronous events, relying on a single virtual address space, and discouraging the use of main memory as an all-purpose synchronization device, preferring instead a specialized inter-core synchronization protocol.

The adoption of a different machine interface comes at the cost of a challenge: most operating software in use today to drive general-purpose hardware, namely operating systems, programming language run-time systems and code generators in compilers have been developed with the assumption that the underlying platform can be modelled by traditional RISC cores with individual MMUs grouped around a shared memory that can be used for synchronization. A port of existing operating software towards the proposed architecture is therefore non-trivial, because the machine interface *conceptually* diverges from established standards. In this dissertation, we investigate the impact of these conceptual changes on operating software. We propose namely answers to the following questions:

- 1. Is it possible to program a chip with the proposed machine interface using an already accepted general-purpose programming language such as C?

- 2. What are the abstract features of the proposed machine interface that make it qualitatively different from contemporary general-purpose processor chips from the perspective of operating software?

The first question is relevant because the availability of existing programming languages is a prerequisite for adoption of a new general-purpose architecture. Moreover, support for C must be available before most higher-level software environments can be reused. For this question our answer is generally positive. By constructing a C compiler and parts of the accompanying language library, we demonstrate that programs following the platform independence guidelines set forth by the designers of C can be reused successfully on multiple instances of the proposed architecture. We also demonstrate how to extend the C language with new primitives that can drive the proposed hardware-based concurrency management protocol. However, we acknowledge that most programs also use system services and make assumptions about the topology and components of the underlying platform. We discuss why some of these assumptions cannot yet be adapted fully transparently to the proposed architecture and suggest a strategy for future work to do so.

The second question is relevant because its answer defines how to advertise the platform to system programmers, who constitute the early technology adopters with the strongest influence. For this question our answer considers separately the various peculiarities of the machine interface.

The proposed ISA provides native hardware support for thread management and scheduling and thus seems to conflict with the traditional role of operating software. Yet as we argue this support does not change existing machine abstractions qualitatively, because concurrency management was already captured in operating software behind APIs with semantics similar to those of the proposed hardware protocol. The machine interface provides configurable numbers of registers per hardware thread, which is a feature yet unheard of in other general-purpose processors. Yet as we show this feature can be hidden completely behind a C code generator, and can thus become invisible to operating system code or higher-level programming languages. The proposed chip topology promotes a single address space shared between processes, relying on capabilities [CLFL94] instead of address space virtualization for isolation, which diverges from the process model of general-purpose operating systems commonly in use today. Yet as we suggest the technology necessary to manage a single virtual address space is already available and widely used (for shared libraries and application "plug-ins") and this feature thus does not pose any new conceptual difficulty.

We found that the first conceptual innovation that warrants further theoretical investigation is the surrender of shared memory as the universal synchronization device for software. In traditional multi-core programming, implicit communication via coherent shared memory locations is routinely abused to provide locking, semaphores, barriers and all manners of time synchronization between concurrent activities. In the proposed architecture, such implicit communication is restricted and new basic programming constructs with fundamentally different semantics must be used instead. We formalize a subset of these semantics, then suggest how they can be used at a higher level in existing concurrent programming languages. To summarize, despite their strong conceptual divergence, we found that these new forms of synchronization are fully general and can theoretically be integrated in existing software, although more work will be needed to actually realize this integration.

The second conceptual innovation we found is the finiteness of concurrency resources. In most implementations of multi-threading on general-purpose platforms, threads and synchronization devices (e.g. mutex locks) are logical concepts instantiated by software, with the assumption that they can be virtualized at will using main memory as a backing store. In the proposed architecture, threads and synchronization devices are finite resources which cause execution deadlock when programs attempt to create more of them than are available in hardware. We argue that thread virtualization is not necessary with the advent of declarative concurrency in programming languages. Unfortunately, we cannot determine whether finiteness of synchronization devices is a net benefit towards further adoption of the architectural concepts. To summarize, we found that this innovation will require further analysis and possibly further refinements of the proposed architecture.

Beyond the scientific contribution towards the two questions outlined above, this book also contains a narrative about the design and implementation of a new processor chip in the midst of contemporary technology challenges. In particular, we highlight that a common trend in processor architecture research is to "solve" conceptual issues by abandoning support for some programming styles and software abstractions. We condemn this trend as being detrimental to true general-purpose computing, and we discuss throughout our dissertation how the requirement to preserve generality in processors impacts development, from the architecture up to applications via operating software.

### Samenvatting

Sinds het begin van de eenentwintigste eeuw hebben energie- en schaalbaarheidsproblemen prestatieverbeteringen van individuele verwerkingseenheden zeer gehinderd [RML<sup>+</sup>01]. Om de spreekwoordelijke Gordiaanse knoop door te hakken heeft de industrie zich sedertdien gericht op het laten toenemen van het aantal verwerkingseenheden per geïntegreerd circuit. Dit heeft tot steeds grotere zgn. multi-processors geleid, waarmee aan (energie)efficiëntie gewonnen kan worden, door middel van het schalen van klokfrequenties [RML<sup>+</sup>01, SA05]. In het ontwerp van zulke multi-processors is het echter nog steeds gebruikelijk algemene verwerkingseenheden, ontworpen voor alleenstaand gebruik, samen te voegen tot een systeem. Een decennium na de herintrede van multi-processors is de computerarchitectuurgemeenschap nog altijd niet tot het inzicht gekomen dat multi-processors ontworpen door het samenstellen van traditionele verwerkingseenheden onvoldoende niet goed programmeerbar zijn voor algemeen gebruik.

De CSA-leerstoel aan de Universiteit van Amsterdam legt zich toe op het ontwikkelen van algemene machinemodellen en beheermodellen voor multiprogrammering, uitgaande van een nieuwe verwerkingseenheid naar eigen ontwerp, die hardwareondersteuning biedt voor de coördinatie van multiprogrammering over meerdere eenheden [PLY<sup>+</sup>12]. Een kernbegrip van deze nieuwe architectuur is "hardwaremicrodeeltaken." Dit begrip omvat asynchronie, d.i. om kunnen gaan met operaties met zeer uiteenlopende verwerkingstijden, fijnmazige hardwarematige deeltaken, een schaalonafhankelijk programmeermodel-welk clusters-op-een-chip van willekeurige omvang als enkelvoudige verwerkingsbronnen behandelt-en een in hoge mate transparante schaalbaarheid van de prestaties van binaire code over variërende clustergroottes. Buiten ingebouwde ondersteuning voor dataflowsynchronisatie en imperatieve parallelle programmeering wijkt deze verwerkingseenheid ook af van het RISC-paradigma op vier gebieden. Het laat programma's zelf bepalen hoeveel hardwarematige registers aan ieder deelproces worden toegewezen. Onderbrekingssignalen worden als primaire asynchrone signalering vervangen door primitieven voor het afsplitsen en samenvoegen van deelprocessen. De programmeur wordt een omvattende virtuele adresruimte aangeboden. Tevens wordt het gebruik van het werkgeheugen als primair synchronisatiemiddel sterk ontmoedigd—ter vervanging is een hiertoe toegespitst synchronisatieprotocol tussen verwerkingseenheden beschikbaar.

De introductie van een dergelijke nieuwe machineinterface heeft behoorlijk wat voeten in de aarde. Gangbare besturingssoftware (besturingssystemen, vertalers, looptijdomgevingen, enz.) veronderstelt veelal, dat de hardware waarop ze wordt uitgevoerd uitwisselbaar is met traditionele RISC eenheden met ieder een individuele MMUs, die allemaal toegang hebben tot hetzelfde werkgeheugen waarmee synchronisatie kan worden gerealiseerd. Dientengevolge kunnen bestaande besturingssystemen niet triviaal worden vertaald naar voornoemde nieuwe architectuur. Het probleem is dat de machineinterface op *conceptueel* niveau afwijkt van gangbare standaarden. Dit proefschrift behandelt de implicaties van deze koerswijziging voor besturingssoftware.

Wij richten ons in dit proefschrift hoofdzakelijk op de volgende vragen:

- 1. Kunnen gangbare programmeertalen, zoals C, worden aangewend om dergelijke verwerkingseenheden te programmeren?

- 2. Wat zijn de kwalitatieve verschillen tussen de voorgestelde machineinterface enerzijds en dat van gangbare algemeen toepasbare processors anderzijds en wat zijn hiervan de implicaties voor besturingssoftware?

De eerste vraag vindt haar relevantie in het gegeven dat de aanvaarding van nieuwe architecturen voor algemeen gebruik veelal sterk afhangt van de overdraagbaarheid van bestaande programmeertalen. In het bijzonder moet C vertaalbaar zijn naar de nieuwe omgeving om menige softwareomgeving te kunnen hergebruiken. In grote lijnen kan deze vraag positief worden beantwoord. Met behulp van een hiertoe ontwikkelde C-vertaler en gedeeltelijk standaard C-bibliotheek kunnen we aantonen dat programma's uitvoerbaar zijn op verschillende instanties van de voorgestelde architectuur, mits deze zijn geschreven volgens de door de C-ontwerpers aangegeven richtlijnen voor platformafhankelijkheid. Tevens breiden we C uit met primitieven die de voorgestelde hardwarematige multiprogrammering aan kunnen sturen. Het behoeft echter vermelding, dat menig concreet programma verdergaande aannames doet over het systeem waarop het wordt uitgevoerd. We behandelen de pijnpunten van de overdraagbaarheid van deze aannames en doen suggesties voor toekomstig onderzoek te dezer zake.

De tweede vraag is relevant, aangezien het antwoord goeddeels bepalend is voor hoe de nieuwe omgeving ten beste aangeboden kan worden aan systeemprogrammeurs. Deze gemeenschap is in hoge mate bepalend voor de verdere aanvaarding van een nieuwe architectuur. De beantwoording van deze vraag gaat dieper in op de verschillende eigenaardigheden van de machineinterface.

De voorgestelde ISA biedt hardwareondersteuning voor het beheer en de planning van deelprocessen, wat ogenschijnlijk botst met de traditionele rol van besturingssoftware. Wij beweren echter, dat het niet (kwalitatief) strijdig is met bestaande machineabstracties, daar het beheer van multi-programmering in besturingssoftware zich normaliter achter APIs verschuilt met een vergelijkbare semantiek. Het machinemodel biedt controle over de toewijzing van het aantal registers aan deelprocessen, wat tot op heden ongehoord is gebleken in algemene verwerkingseenheden. Desalniettemin tonen wij aan dat deze eigenschap kan worden verhult door toepassing van een C-codegenerator, waardoor noch besturingssysteem, noch enige programmeertaal op een hoger abstractieniveau hier enige hinder van ondervindt. De voorgestelde chiptopologie biedt processen allemaal dezelfde adresruimte. Hier vindt toegangscontrole plaats op basis van geschiktheid [CLFL94], in plaats van virtualisatie van de adresruimte. Deze aanpak wijkt af van de procesmodellen van moderne, gangbare, algemene besturingssystemen. Evenwel wijzen we op de beschikbaarheid van gebruikelijke technologie voor het beheer van dergelijke onverdeelde adresruimten (zoals, bijvoorbeeld, voor gedeelde bibliotheken en dynamische programmauitbreidingen) die op vergelijkbare wijze kunnen worden toegepast, waardoor er geen conceptuele obstakels worden geboden.

De eerste conceptuele innovatie, waaruit verdere theoretische onderzoeksvragen voortkomen, is het loslaten van het idee om het gedeelde werkgeheugen als synchronisatiemechaniek aan te wenden voor software. Traditionele multiprogrammeringsmethoden implementeren doorgaans abusievelijk met gedeelde variabelen wederzijdse uitsluiting, semaforen, synchronisatiebarrières en velerlei andere synchronisatiemechanismen tussen verschillende taken. De voorgestelde architectuur stelt paal en perk aan dit soort communicatie en biedt ter vervanging basis programmeerconcepten met fundamenteel andere semantiek. Een deel van deze semantiek wordt in dit proefschrift geformaliseerd en de toepassing van deze concepten in bestaande programmeertalen op hoger niveau wordt toegelicht. Samenvattend beweren wij dat, ondanks conceptuele afwijkingen, deze nieuwe synchronisatiemechanieken niets inboeten aan algemeenheid en theoretisch geïntegreerd kunnen worden met bestaande software, alhoewel voor dit laatste meer werk noodzakelijk is.

De tweede conceptuele innovatie die we presenteren is de eindigheid van de ondersteunende middelen voor multiprogrammering. Verreweg de meeste implementaties van algemene, multiprogrammeerbare systemen zien deeltaken en synchronisatiemechanieken (b.v. semaforen) als logische concepten die door software worden geïnstantieerd. Hierbij wordt aangenomen dat ze onbeperkt kunnen worden gevirtualiseerd in het werkgeheugen. In de voorgestelde architectuur zijn deze middelen eindig, waardoor programma's vastlopen wanneer ze zich meer dan in de hardware beschikbare middelen proberen toe te kennen. Wij bepleiten echter, dat met de opmars van declaratieve multiprogrammering in programmeertalen deze virtualisatiebehoefte teniet doet. Helaas kunnen we niet inschatten of de eindigheid van synchronisatiemechanieken de aanvaarding van deze architectuur in de vakgemeenschap in de weg zal staan. Samenvattend kunnen we stellen dat deze innovatie verder zal moeten worden onderzocht en dat de voorgestelde architectuur mogelijk zal moeten worden bijgestuurd.

Buiten de wetenschappelijke bijdragen omtrent de bovengenoemde vragen omvat dit proefschrift ook een relaas over het ontwerp en de implementatie van nieuwe verwerkingseenheden, te midden van hedendaagse technologische uitdagingen. We benadrukken in het bijzonder, dat recente onderzoeken naar architecturen van verwerkingseenheden meestal neigen naar het loslaten van het bieden van ondersteuning voor gevestigde programmeerstijlen en softwareabstracties om conceptuele problemen "op te lossen." Deze neiging wijzen wij af, als zijnde schadelijk voor algemeen computergebruik. Als rode draad door dit proefschrift loopt ons pleidooi voor het behoud van algemeenheid in verwerkingseenheden en de consequenties hiervan voor ontwikkeling, van architectuur, via besturingssysteem, tot aan toepassingen.

### Dankwoord / Acknowledgements

#### In memoriam: Bertrand Russell, Dennis Ritchie & de kat

Zo'n onderneming van meerdere jaren, met zo weinig zekerheid op voorhand over de uiteindelijke resultaten, kan worden vergeleken met het opvoeden van een kind of met een zelf-ontdekkingsreis. Zo heb ik het wel gedeeltelijk ervaren; al was mijn project een zoektocht naar het onderliggende netwerk van kennissen, culturen, vaardigheden en methoden die aan het bouwen van een computersysteem ten grondslag ligt. Op zoek naar een waarheid die ik kon erkennen, heb ik dankbaar hulp aanvaard tijdens mijn oorlog tegen foute aannames, onvolledige argumenten, drogredenen en andere vormen van onwetendheid.

Deze ervaring durf ik te vergelijken met de cursus stijldansen waarvan ik vele zondagen gedurende mijn onderzoek genoot. Mijn meest betrouwbare danspartner is zonder twijfel Mike Lankamp geweest. Vier jaar lang hebben wij samen een genadeloze tango gedanst, altijd in strijd met elkaar, waarbij de rollen van leider en volger regelmatig wisselden, maar waarbij we altijd samen toe werkten naar een esthetisch elegant resultaat. Our training was faithfully guided by Chris Jesshope, who, beyond playing the background scientific tune to which we danced, also subtly gave the measure, provided us with first steps to follow, and trusted us to "make things happen" on our own. I will be forever grateful to both for this lasting learning experience.

While exercising, I have also learned much from working with my fellow dancers and elders: Irfan, Jian, Joe, Jony, Kostas, Michael and Qiang, you have been inspiring examples. Vooral Thomas en Michiel hebben mij vaak geholpen met de knepen van het vak en persoonlijke coaching; ik ben jullie hiervoor bijzonder dankbaar. Wij deelden ook de vloer met collega's die een andere stijl dansten. Al leek hun muziek op de onze, toch waren de pasjes net iets anders; door naar hen te kijken heb ik mijn eigen kunnen verbeteren. Daarom wil ik mijn respect uitspreken voor Andy, Clemens, Fangyong, Mark, Merijn, Peter, Roberta, Roeland, Roy, Toktam en Wei alsmede hen bedanken. Similarly, I cherished our joint learning with partners from other schools: Bodo, Carl, Dan, Dimitris, Frank, George, Jara, Leoš, Lukas, Martin, Raimund and Stephan, although you exercised a different swing on the same music, the experience would have been largely incomplete without you.

Naturally, I would like to also thank respectfully the members of the evaluation committee, namely professor Jesshope, dr. Chamberlain, professor Scholz, dr. Grelck, professor de Laat, professor Brorsson, and professor Klint, for their extensive comments and suggestions toward improving the earlier versions of this book.

Ondanks mijn liefde voor het dansen en mijn interesse voor de muziek van Chris, had ik het niet zo lang vol kunnen houden zonder de betrokkenheid en ondersteuning van een paar waardevolle en bijzondere personen. In de eerste plaats Rob Jelier, wie mij de weg van een promotie wees. Van Rob kreeg ik een vernieuwd geloof in de wetenschap, en ook in mijzelf. Door zijn voorbeeld te volgen, heb ik mijn grondgedachten onderzocht, mijn dieptepunt van onzekerheid bereikt en ontdaan van alle externe motivaties. Toch ging ik door, gedreven door pure nieuwsgierigheid. Naast Rob zijn Mark Thompson en Simon Polstra trouwe vrienden geworden die me voortdurend aan herinnerden dat ik niet slechts een wetenschappelijk instrument ben, en dat mijn irrationele behoeften als mens ook aandacht verdienen. Want ondersteuning op het menselijke vlak had ik natuurlijk ook nodig: die heb ik niet alleen gekregen van Rob, Mark en Simon, maar ook van Marseda Duma, Sabien Jesse, Roberta Piscitelli, Arnold Pols and Sylvain Viollon, die er altijd voor me waren wanneer motivatie ontbrak. En toen de tijd kwam om na te deken over wat ik "erna" ging doen, heeft Merijn Verstraaten mij geholpen om een nieuwe betekenis aan mijn rol te geven; dankzij hem heb ik het afronden van het werk kunnen ervaren meer als een overgang dan een eindstreep. Zonder jullie was het werk en daarmee ook dit boek nooit afgekomen.

Verder is mijn werk ontzettend verrijkt door een paar onwaarschijnlijke ontmoetingen. Dankzij Marjolein op den Brouw heb ik begrepen dat wetenschappelijke onderzoek een zeer persoonlijke onderneming is, onafhankelijk van de voorkeuren van collega's en promotor(e)(s). Both Marjolein and Daniel Prokesch have taught me how inspiration and curiosity come from within and must often be carefully balanced with other life priorities. Het begrip dat onderzoek en onderwijs niet veel meer dan een sociaal spel zijn, met eigen politieke regels, leerde ik ten eerste van Philip Hölzenspies; van hem, en ook van Jan Kuper, leerde ik tegelijkertijd dat "het spel" leuk kan blijven, zolang de deelnemers ervan weten te genieten. Ik dank jullie beide voor de wijze les om vaker te focussen op wat voor mij leuk is.

Last but not least, I wholeheartedly dedicate a kind word to Stephan Herhut, Andrei Matei, Frank Penczek and Merijn Verstraaten. Despite, or perhaps thanks to, our contrasting personalities and quite distinct perspectives, you have provided a true meaning to the words "community of peers." With you I have simultaneously enjoyed the feeling of mutual interest, admiration, pride and respect, the excitement of working and learning together, and a healthy dosis of mutual evaluation and competition. I am looking forward to building our friendships further.

kena Amsterdam, July 2012

### Preface

Zonder verhaal zijn feiten sprakeloos.

Karel van der Toorn

When I joined the CSA group in September 2008, my supervisor Chris Jesshope tasked me thus: "We made this novel chip called a Microgrid, and we want a C compiler to program it. Do it."

This is most of what this book is about. You are now holding a report on four years worth of work towards compiling and running C programs on Microgrids, which are multicore, multithreaded processor chips. I am proud and content to report that a C compiler now exists for this architecture. The following pages will hopefully convince you that the corresponding software technology and example uses constitute an adequate answer to my supervisor's request.

Meanwhile, these four years have been intellectually instructive.

The first and most prominent discovery was that these Microgrid chips, that needed a compiler, lacked a specification when my work started. As I learned quickly, there are two meanings for the word "exist" in computer architecture. One definition, commonly used by the layman, suggests a working physical artifact. This definition, however, is quite uncommon in the research field: most chip architectures "exist" instead as *models* (blueprints) that can be studied analytically or via software simulations. The Microgrid architecture obviously did not exist in this first sense, as it was not expected anyway. My surprise, instead, was to realize that Microgrids only "existed" in the other sense in the *mind* of my colleagues. Their existence was vernacular, shapeshifting, and lacked committed documents that I could study and refer to. The second, most exciting discovery was that my colleagues had not invented *one* chip design but instead a *class* of chip designs, which could be instantiated over a range of design parameters. Therefore, to make a compiler, I first had to capture my colleague's minds on paper, then understand the architecture class so that a C compiler could target all its possible instances.

On this quest to gather such a *generic platform specification*, a prerequisite to implement a compiler, I made two further discoveries:

- previously written information about the new architecture was inconsistent, i.e. it expressed conflicting ideas;

- the unwritten intellectual model manipulated by my peers, while relatively consistent, was largely insufficient to implement a C compiler and accompanying software. For example, it missed the concept of external input and output.

In other words, the task initially assigned to me required that I first document the meta-architecture and then an instance thereof in sufficient detail. It also required that I complement the model with additional features required by the new software. While doing this, I had to accommodate the fact that some system features required to compile the C language are not technically part of a compiler nor the hardware architecture, but rather the "environment" provided by a software operating system. Therefore I had to also contribute some additional technology in that direction. All this happened, although as you would probably agree these steps are somewhat difficult to capture behind a simple "problem statement" such as found in most doctoral theses.

When I wrote the first version of this book, its narrative was similar to the steps outlined above and amounted to a straightforward technical report. When I initially submitted this report, my supervisor rejected it. He argued that the *scientific* community would not be interested in an engineering story; that they would rather like to understand which *new knowledge* I had created on my way. So I sat and mulled over the report. What did I learn during this work? What new knowledge did I create that was worth sharing?

At the foreground, surely there was some knowledge to share about the creation and exploitation of a C compiler for a new architecture. So I left that in, to be found in chapters 6, 8 to 11 and 13. Yet I found that sharing *only* this knowledge was oddly unsatisfying, because it depended on knowledge about said new architecture that was either unpublished or inconsistent, and somewhat incomplete. Therefore, I decided to *also* share the detailed knowledge I gathered from my colleagues about their Microgrid meta-model, complemented by details about the different concrete instances that I used in my work. And so I added that knowledge to the text, to be found in chapters 3 to 5. As a welcome side effect of this excercise, I was also able to argue towards a *renewed motivation* (chapter 2) for the architecture design, to complement the 15 years old argument [BJM96] that had so far served unchanged as justification for the line of work.

When this was done, I mulled again: although I had formulated new knowledge and made a scientific contribution to my field, I had not yet done justice to what I had found most important and fundamental in those four years. For there were two other aspects, which I dare call "knowledge" although my supervisor calls them "experience," that I had also isolated. The first is my understanding of the thrust of practitioners in my field: what *innovation* really means in computer architecture and why it is so crucially important to the future of computing. I share my views on this topic in chapters 1 and 16; this explains why you should care about my story, even though you may not be interested in Microgrids specifically. The second is my understanding of an obstacle shared between computer architects working on multi-core chip designs, that is the necessary disruption of unspoken knowledge.

Beyond the immediate need for more performance per watt, the role of a processor chip designer is to provide components to other humans to use in larger systems; as such, there is an iterated step of human-to-human communication required between component architects, system architects and software practitioners. Due to the largely technical nature of the devices considered, this communication is necessarily dense; to reduce verbosity, the people involved rely on unspoken, tacit knowledge constituted by their cultural background in computer science. *Innovation is difficult because of this reliance on tacit knowledge*. Any novel component will break some unspoken assumptions and invalidate some commonly accepted "truths." Innovation thus requires formulating a new cultural background about hardware platforms, a step which most audiences—especially in the software world—are ill-trained to perform. In the case of Microgrids, my colleagues had already discovered that the mere prospect of additional performance is not enticing enough when its cost is a necessarily more complex mental model of the machine. What I have understood however, is that software audiences are willing to pay the price of more complex models if *they believe that they gain in flexibility*, i.e. future increases in productivity. There are two requirements to support this belief. The first is that the chip designer *does not gratuitously remove features* previously relied upon; the second is that the chip designer argues for the *generality* of any new features, to convince software audiences they can be used in ways not yet foreseen. As I found out, these two requirements were previously not very well addressed in the work around Microgrids. To my colleagues' defense, neither are they in other research projects in computer architecture. Nevertheless I believe they are still essential to the eventual fruition of innovative research in the field.

To advertise this experience, I thus decided to spend extra care to:

- detail the proposed architecture from the perspective of system software (chapters 3 and 4), highlight some of the most affected assumptions about the underlying machine model (chapter 7), and suggest how features commonly found in other platforms are also found in the proposed design (chapters 5 and 14);

- argue for generality throughout, starting with a renewed defense of general-purpose computing (chapter 1) and placing emphasis on the potential use of the platform by contemporary concurrent programming models (chapters 7, 9 and 12).

With this extra effort I want to communicate that the concepts around the advent of Microgrids are not merely the bread and butter of a small research group; that this research answers general requirements that deserve attention regardless of which specific architecture they are considered from. This is why chapters 3, 4 and 9 are longer than strictly required by a platform specification towards a C compiler, and why chapters 5, 7, 12 and 14 do not fit the purely technical line of thought of the other chapters. As I explain in section 1.7, this "meta-thesis" provides a second reading level, distinct from the technical contribution at the first level.

To keep a long story short, if you wish to restrict your reading to the joys of compiling C towards Microgrids, you can narrow down your focus to chapters 6, 8 to 11 and 13. The rest is "simply" *philosophy*.

## Chapter 1 Introduction

Ingenuity and imagination, rather than accurate thought, are the ordinary weapons of science.

G.H. Hardy [Har11].

#### Contents

| 1.1 | Birdview epistemology 16               |

|-----|----------------------------------------|

| 1.2 | Computer science                       |

| 1.3 | Stem cells of computing                |

| 1.4 | Losing sight of generality             |

| 1.5 | Achilles' heel of designers            |

| 1.6 | Case study: hardware microthreading 28 |

| 1.7 | Overview                               |

#### 1.1 Epistemology: science is team work, so is innovation

The traditional purpose of the fundamental sciences is the acquisition of new knowledge pertaining to observed phenomena, in an attempt to describe "what is." In parallel to the discovery of new knowledge through scientific inquiry, philosophers, or theoreticians, derive ideas of "what could be." Via formalisms, they construct structures of thought to validate these ideas and derive iteratively new ideas from them.

We can focus for a moment on the human dynamics around these activities. On the one hand, the intellectual pleasure that internally motivates the human scientists is mostly to be found in the acquisition of knowledge and ideas. For natural scientists, the focus is on accuracy relative to the observed phenomena, whereas for philosophers the focus is on consistency. On the other hand, the external motivation for all fields of science, which materially sustains their activities, is the need of humans for either discovery or material benefits to their physical existence. From this position, the outcome of scientific inquiry and philosophical thought, namely knowledge and ideas, is not directly what human audiences are interested in. The "missing link" between scientific insight and its practical benefits is *innovation*, an *engineering* process in two steps.

The first step of innovation is *foundational engineering*: the creative, nearly artistic process where humans find a new way to assemble parts into a more complex artifact, following the inspiration and foreshadowing of their past study of knowledge and ideas, and guided by human-centered concerns. Foundational engineering, as an activity, consumes refined matter from the physical world and produces new more complex things, usually tools and machines, whose function and behavior are intricate, emergent composition of their parts. The novelty factor is key: the outcome must have characteristics yet unseen to qualify as foundational; merely reproducing the object would just qualify as manufacturing. The characteristic human factor in this foundational step is *creativity*, which corresponds to the serendipitously successful, mostly irrationally motivated selection of ideas, knowledge and material components in a way that only reveals itself as useful, and thus can only be justified, a posteriori.

The other step is *applicative engineering*, where humans assemble artifacts previously engineerd into complex systems that satisfy the needs of fellow humans. In contrast to foundational engineering, the characteristic human factor here is meticulousness in the realization and scrupulousness in recognizing and following an audience's expectations—if not fabricating them on the spot.